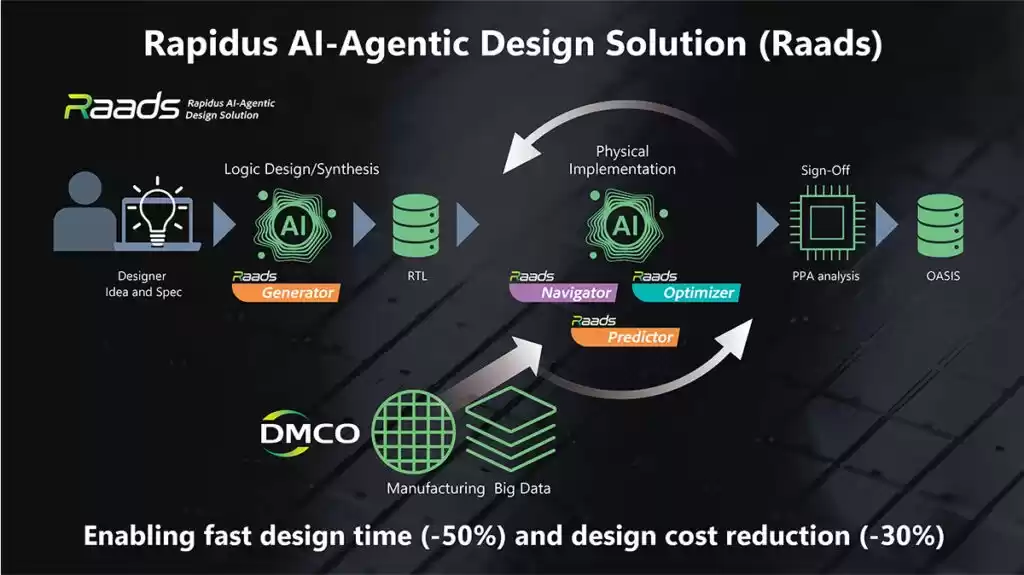

2025年12月17日,Rapidus公司宣布推出一套名為「Raads」的工具,旨在推廣其快速統一製造服務(RUMS)。這些工具將從2026財年開始陸續發布。 Raads包含多個工具,並將與製程設計工具包(PDK)和參考流程一起提供給客戶。該工具最初名為“Rapidus AI輔助設計解決方案”,未來將發展成為“Rapidus AI智慧設計解決方案”。將Raads與現有EDA工具結合使用,可實現設計時間縮短50%,設計成本降低30%。

該公司的主要工具包括基於LLM的EDA工具“Raads Generator”和RTL調試及物理設計/佈局佈線優化工具“Raads Predictor”。該公司計劃未來發布「Raads Navigator」、「Raads Indicator」、「Raads Manager」和「Raads Optimizer」。到2025年6月,該公司的IIM-1將連接全球200多台最先進的單晶圓半導體製造設備,並將開始2nm GAA電晶體的原型製作和運行驗證。

從: ![]() Rapidus 將其獨特的基於人工智慧的「Raads」概念付諸實踐——按順序發佈設計支援工具

Rapidus 將其獨特的基於人工智慧的「Raads」概念付諸實踐——按順序發佈設計支援工具

【社論】

在日本半導體產業復興的歷史背景下,Rapidus 的人工智慧設計工具「Raads」具有超越單純技術創新的戰略意義。

半導體設計面臨的最大瓶頸是設計週期過長和成本不斷上漲。隨著2nm製程的日益普及,傳統的EDA(電子設計自動化)工具給設計人員帶來了沉重的負擔。 Rapidus新推出的Raads正是為了應對這項挑戰而生,它提供了一套全面的設計支援工具,利用了LLM(大規模語言模型)和機器學習技術。

尤其值得注意的是概念從「AI輔助」到「AI代理」的轉變。這意味著AI不再只是輔助工具,而是作為「代理」積極參與設計過程。當設計人員輸入規格時,Raads Generator會自動產生針對Rapidus 2nm製程最佳化的RTL(暫存器傳輸級)設計數據,而Raads Predictor則可以快速預測PPA(功耗、效能、面積)。

透過這套系統,Rapidus設定了具體的量化目標,即設計時間縮短50%,設計成本降低30%,將對半導體產業產生巨大影響。在與台積電和三星等現有主要晶圓代工廠的競爭中,Rapidus在技術節點方面略遜一籌,但它正試圖透過大幅縮短從設計到製造的周期來脫穎而出。

Rapidus 的優勢在於其 IIM-1 工廠採用的單晶圓製程。與傳統的批量處理不同,逐片處理晶圓能夠收集更詳細的數據,這些數據隨後用於訓練人工智慧模型。到 2025 年 6 月,該公司將連接超過 200 台尖端設備。今年 7 月,該公司開始對 2nm GAA 電晶體進行原型開發,並成功驗證了其運行,展現了其驚人的速度。

然而,挑戰依然存在。 Rapidus的目標是在2027年開始量產,但屆時台積電可能已經過渡到下一代製程節點。此外,在吸引客戶方面,與成熟的晶圓代工廠競爭也將十分困難。不過,開發像Raads這樣的自主人工智慧設計工具,並將其與PDK(製程設計套件)捆綁銷售,不失為一種降低設計門檻、吸引更多客戶的明智策略。

日本政府已決定提供約1.72兆日圓的資金支持,這表明其將振興半導體產業作為國家戰略。另有報道稱,IBM的工程師已被派往北海道的工廠,作為技術合作的一部分,這表明技術轉移正在穩步推進。

Raads的真正價值或許在於其半導體設計的普及化。透過利用人工智慧技術,Raads使中小企業和新創公司也能設計出以往只有少數大型企業才能掌握的尖端工藝,從而有望拓寬創新的範圍。

[術語]

RTL(暫存器傳輸級)

在半導體設計中,抽象層級是指將數位電路的運作描述為暫存器之間的資料傳輸。它使用硬體描述語言(例如 Verilog 或 VHDL)編寫,並使用邏輯綜合工具轉換為閘級電路。設計人員可以在高層定義電路的功能,而無需關心物理實現的細節。

EDA(電子設計自動化)

EDA(電子設計自動化)是支援半導體晶片設計、驗證和製造準備的軟體工具的總稱。它能夠自動化晶片設計的各個流程,包括電路圖創建、邏輯綜合、佈局佈線和時序驗證。 Synopsys、Cadence 和 Siemens EDA 是業界的領導者。對於當今包含數十億個電晶體的複雜半導體設計而言,EDA 至關重要。

PDK(製程設計工具包)

針對特定製造流程的設計資料包,包含裝置模型、設計規則、標準單元庫等。設計人員可利用此資料包設計可製造的電路。該資料包由代工廠提供,是連接設計與製造的重要橋樑。

PPA(電力性能區)

半導體設計中有三個重要的評估指標:功耗(功耗)、性能(性能/運行速度)和麵積(晶片面積)。這三者之間存在權衡關係,設計人員必須根據應用找到最佳平衡點。人工智慧設計工具可以自動完成此功耗、效能和麵積(PPA)最佳化。

GAA(全包圍柵極)電晶體<br>新一代電晶體結構之一,其閘極環繞通道的整個外圍。與傳統的FinFET相比,它具有更好的閘極可控性,從而可以進一步縮小尺寸。台積電和三星也將其作為2nm及以下製程的關鍵技術。

LLM(大型語言模型)

這是一個基於海量文字資料訓練的大規模神經網路模型。它能夠理解和產生自然語言,並應用於 ChatGPT 等專案中。 Rapidus 使用 LLM 從半導體設計規格產生 RTL 程式碼。

單晶圓加工

這種製造方法逐片處理晶圓。與傳統的批量處理不同,它可以收集每片晶圓的詳細數據。 Rapidus 已將這種方法應用於所有生產流程,並利用人工智慧技術進行最佳化。

RUMS(快速統一製造服務)

Rapidus 是一種新型的晶圓代工服務模式,它整合了設計、晶圓製造和 3D 封裝,從而縮短了週期時間。其獨特的方法將單晶圓製程與人工智慧設計工具結合。

2nm製程<br>半導體製造領域最先進的製程技術。電晶體閘極寬度標稱值為2奈米(與實際物理尺寸不同)。據稱,其效能比7nm晶片提升45%,能源效率提升75%。台積電將於2025年開始量產,而Rapidus的目標是2027年。

[參考連結]

Rapidus 公司(外部)

成立於 2022 年的日本半導體代工廠。該公司目前正在北海道千歲市建造一座 2nm 相容工廠 IIM-1。

IBM研究院 – 半導體(外部)

IBM的半導體研究部門。致力於開發2奈米以下節點晶片及3D奈米片電晶體技術。

Synopsys (外部)

全球最大的EDA工具供應商,提供包括邏輯綜合、驗證和實體設計在內的綜合工具。

Cadence 設計系統(外部)

EDA產業第二大公司,在佈局佈線、類比電路設計和驗證工具方面實力雄厚。

台積電(台灣半導體製造有限公司) (外部)

全球最大的半導體代工廠計劃於 2025 年開始大規模生產 2nm 製程。

[參考文章]

Rapidus發布用於先進半導體製造的全新AI設計工具(外部連結)

Rapidus 官方英文新聞稿,詳細介紹了 Raads 工具套件和數值目標。

Rapidus公司在2nm GAA晶體管原型製作方面取得重大里程碑(外部訊息)

公佈2025年7月里程碑:宣布設備連接完成和2nm原型成功。

日本Rapidus公司將與台積電和三星爭奪晶片霸主地位(外部報告)

分析 Rapidus 的策略定位,探討單晶圓製程的優勢及其對日本半導體復興的意義。

Rapidus 展示 2nm 晶片原型,目標是在 2027 年實現量產(外部連結)

據報道,該公司計劃將產能從每月 7,000 張提高到 25,000-30,000 張。

[編者註]

隨著日本半導體產業再次躋身世界領先地位,Rapidus 的挑戰向我們每個人提出了問題:人工智慧時代需要什麼樣的半導體?設計和製造方法應該如何改變?

Raads 致力於採用與台積電和三星不同的方法,大幅縮短設計週期,這也為技術民主化開闢了新的可能性。您如何看待這項國家級計畫的未來? innovaTopia 編輯團隊將持續關注該項目,直至 2027 年量產啟動。